# QSFP28 100GBASE-LR4 1310nm **10km Industrial Transceiver**

OSFP28-LR4-100G-I

## Application

• 100GBASE-LR4 100G Ethernet, Telecom

## **Features**

- Compliant with QSFP28 Standard:SFF-8665

Maximum power consumption 4.5W Revision 1.9, SFF-8636 Revision 2.6

- Compliant with IEEE 802.3ba 100GBASE-LR4

LAN WDM EML laser and PIN Receiver Array

Complies with EU Directive 2011/65/EU

- High speed I/O electrical interface (CAUI-4) compliant with IEEE 802.3bm

- -40~85 °C Case Operating Temperature

- QSFP28 MSA package with duplex LC connector

- Two Wire Serial Interface with Digital **Diagnostic Monitoring**

- (RoHS compliant)

- Single 3.3V Supply Voltage

- Class 1 Laser

## **Product Specifications**

## I. Absolute Maximum Ratings

| Parameter                              | Symbol                  | Min  | Тур. | Мах     | Unit | Ref. |

|----------------------------------------|-------------------------|------|------|---------|------|------|

| Storage Temperature                    | Ts                      | -40  |      | +85     | °C   |      |

| Supply Voltage                         | Vcc                     | -0.5 |      | 3.6     | V    |      |

| Operating Humidity<br>(non-condensing) | RH                      | 5    |      | 95      | %    |      |

| Data Input Voltage – Differential      | $IV_{DIP}$ - $V_{DIN}I$ |      |      | 1.0     | V    |      |

| Control Input Voltage                  | V <sub>1</sub>          | -0.3 |      | Vcc+0.5 | V    |      |

| Control Output Current                 | Ι <sub>ο</sub>          | -20  |      | 20      | mA   |      |

## II. Recommended Operating Environment

| Parameter                                    | Symbol             | Min   | Тур.    | Max   | Unit | Ref.    |

|----------------------------------------------|--------------------|-------|---------|-------|------|---------|

| Operating Case Temperature                   | T <sub>OPR</sub>   | -40   |         | 85    | °C   |         |

| Power Supply Voltage                         | Vcc                | 3.135 | 3.3     | 3.465 | V    |         |

| Instantaneous peak current at hot<br>plug    | I <sub>CC IP</sub> |       |         | 1800  | mA   | Per pin |

| Sustained peak current at hot plug           | I <sub>CC SP</sub> |       |         | 1485  | mA   | Per pin |

| Maximum Power Dissipation                    | P <sub>DLP</sub>   |       |         | 4.5   | W    |         |

| Maximum Power Dissipation,<br>Low Power Mode | P <sub>DLP</sub>   |       |         | 1.5   | W    |         |

| Aggregate Bit Rate                           | ABR                |       | 103.125 |       | Gb/s |         |

| Data Rate per Lane                           | DRL                |       | 25.78   |       | Gb/s |         |

| Control Input Voltage High           | V <sub>IH</sub> | V <sub>CC</sub> *0.7 |     | V <sub>CC</sub> +0.3 | V    |             |

|--------------------------------------|-----------------|----------------------|-----|----------------------|------|-------------|

| Control Input Voltage Low            | V <sub>IL</sub> | -0.3                 |     | V <sub>CC</sub> *0.3 | V    |             |

| Two Wire Serial Interface Clock Rate |                 |                      |     | 400                  | kHz  |             |

| Power Supply Noise                   |                 |                      |     | 66                   | mVpp | 10Hz -10MHz |

| Rx Differential Data Output Load     |                 |                      | 100 |                      | ohms |             |

| <b>Operating Distance</b>            |                 | 2                    |     | 10000                | m    |             |

# III. Optical Characteristics

| Parameter                                   | Symbol               | Min     | Тур.    | Мах     | Unit | Ref. |  |  |  |

|---------------------------------------------|----------------------|---------|---------|---------|------|------|--|--|--|

| Transmitter                                 |                      |         |         |         |      |      |  |  |  |

| Wavelength L0                               | $\lambda_{C0}$       | 1294.53 | 1295.56 | 1296.59 | nm   |      |  |  |  |

| Wavelength L1                               | $\lambda_{C1}$       | 1299.02 | 1300.05 | 1301.09 | nm   |      |  |  |  |

| Wavelength L2                               | $\lambda_{C2}$       | 1303.54 | 1304.58 | 1305.63 | nm   |      |  |  |  |

| Wavelength L3                               | $\lambda_{C3}$       | 1308.09 | 1309.14 | 1310.19 | nm   |      |  |  |  |

| Side-mode suppression ratio                 | SMSR                 | 30      |         |         | dB   |      |  |  |  |

| Total Average Optical Launch<br>Power       | P <sub>OUT</sub>     |         |         | 10.5    | dBm  |      |  |  |  |

| Average Launch Power Tx_Off<br>(Each Lane)  | P <sub>OUT_OFF</sub> |         |         | -30     | dBm  |      |  |  |  |

| Average Optical Launch Power<br>(Each Lane) | P <sub>OUTL</sub>    | -4.3    |         | 4.5     | dBm  |      |  |  |  |

| <b>Extinction Ratio</b>                     | ER                   | 4       |         |         | dB   |      |  |  |  |

| Spectral Width                              | Δλ                   |         |         | 1       | nm   |      |  |  |  |

| <b>6</b> F | S |

|------------|---|

|------------|---|

| Optical Modulation Amplitude<br>(Each Lane)                  | OMA                     | -1.3     |                 | 4.5     | dBm   |  |

|--------------------------------------------------------------|-------------------------|----------|-----------------|---------|-------|--|

| Launch Power in OMA minus TDP<br>(Each Lane)                 | OMA-TDP                 | -2.3     |                 |         | dBm   |  |

| Difference in launch power<br>between any two lanes<br>(OMA) | DT_OMA                  |          |                 | 5       | dB    |  |

| Transmitter and Dispersion<br>Penalty (Each Lane)            | TDP                     |          |                 | 2.2     | dB    |  |

| Optical Return Loss Tolerance                                | ORLT                    |          |                 | 20      | dB    |  |

| Transmitter Eye Mask Definition                              |                         |          | IEEE 802.3ba-20 | 010     |       |  |

| <b>Relative Intensity Noise</b>                              | RIN                     |          |                 | -130    | dB/Hz |  |

|                                                              |                         | Receiver |                 |         |       |  |

| Wavelength L0                                                | $\lambda_{CO}$          | 1294.53  | 1295.56         | 1296.59 | nm    |  |

| Wavelength L1                                                | $\lambda_{C1}$          | 1299.02  | 1300.05         | 1301.09 | nm    |  |

| Wavelength L2                                                | $\lambda_{C2}$          | 1303.54  | 1304.58         | 1305.63 | nm    |  |

| Wavelength L3                                                | $\lambda_{C3}$          | 1308.09  | 1309.14         | 1310.19 | nm    |  |

| Receiver Sensitivity (OMA) per<br>Lane                       |                         |          |                 | -8.6    | dBm   |  |

| Stressed Receiver Sensitivity in<br>OMA (Each Lane)          |                         |          |                 | -6.8    | dBm   |  |

| Stressed Receiver Sensitivity Test<br>Conditions:            |                         |          |                 |         |       |  |

| Stressed Eye J2 Jitter<br>(Each Lane)                        |                         |          | 0.3             |         | UI    |  |

| Stressed Eye J9 Jitter<br>(Each Lane)                        |                         |          | 0.47            |         | UI    |  |

| Vertical Eye Closure Penalty                                 |                         |          | 1.8             |         | dB    |  |

| Damage Threshold for Receiver                                | P <sub>in, damage</sub> | 5.5      |                 |         | dBm   |  |

| Average Receive Power<br>(Each Lane)                         |                         | -10.6    |                 | 4.5     | dBm   |  |

| Receive Power in OMA (Each Lane),<br>Overload                  | OMA             |  | 4.5 | dBm |  |

|----------------------------------------------------------------|-----------------|--|-----|-----|--|

| Difference in receive power between<br>any two lanes (OMA)     | DR_OMA          |  | 5.5 | dB  |  |

| Receiver 3dB electrical upper cut-off<br>frequency (each lane) | F_C             |  | 31  | GHz |  |

| <b>Receiver Reflectance</b>                                    | RX <sub>R</sub> |  | -26 | dB  |  |

#### Note:

1. Measured with a PRBS2<sup>31</sup>-1 test pattern @25.78125Gbps, BER≦10<sup>-12</sup>

## **IV. Electrical Characteristics**

High-Speed Signal:Compliant to CAUI-4 (IEEE 802.3bm)Low-Speed Signal:Compliant to SFF-8679

| Parameter                             | Symbol               | Min     | Тур. | Мах                  | Unit | Ref. |  |  |

|---------------------------------------|----------------------|---------|------|----------------------|------|------|--|--|

| Transmitter                           |                      |         |      |                      |      |      |  |  |

| Differential Data Input<br>Amplitude  | V <sub>IN,P-P</sub>  | 95      |      | 900                  | mVpp | 1    |  |  |

| Differential Termination<br>Mismatch  |                      |         |      | 10                   | %    |      |  |  |

| LPMode, Reset and ModSelL             | V <sub>IL</sub>      | -0.3    |      | 0.8                  | V    |      |  |  |

| LF MOUE, RESEL AND MOUSEL             | V <sub>IH</sub>      | 2       |      | V <sub>CC</sub> +0.3 | V    |      |  |  |

|                                       |                      | Receive | r    |                      |      |      |  |  |

| Differential Data Output<br>Amplitude | V <sub>OUT,P-P</sub> | 250     |      | 900                  | mVpp | 1    |  |  |

| Differential Termination<br>Mismatch  |                      |         |      | 10                   | %    |      |  |  |

| Output Rise/Fall Time,<br>20%~80%     | T <sub>R</sub>       | 9.5     |      |                      | ps   |      |  |  |

| ModPrsL and IntL | V <sub>OL</sub> | 0                    | 0.4                  | V | I <sub>OL</sub> =4mA  |

|------------------|-----------------|----------------------|----------------------|---|-----------------------|

|                  | V <sub>OH</sub> | V <sub>cc</sub> -0.5 | V <sub>CC</sub> +0.3 | V | I <sub>OL</sub> =-4mA |

#### Note:

1. Amplitude customization beyond these specs is dependent on validation in customer system.

## V. Digital Diagnostic Monitoring Information

| Parameter                   | Range                | Accuracy | Unit | Calibration |

|-----------------------------|----------------------|----------|------|-------------|

| Temperature                 | -5 to 85             | ±3       | °C   | Internal    |

| Voltage                     | 0 to $V_{\text{CC}}$ | 0.1      | V    | Internal    |

| Tx Bias Current (Each Lane) | 0 to 100             | 10%      | mA   | Internal    |

| Tx Output Power (Each Lane) | -4.3 to 4.5          | ±3       | dB   | Internal    |

| Rx Power (Each Lane)        | -10.6 to 4.5         | ±3       | dB   | Internal    |

### VI. Timing

#### **Timing for QSFP+ Soft Control and Status Functions**

| Parameter                      | Symbol       | Min | Тур. | Мах  | Unit | Ref. |

|--------------------------------|--------------|-----|------|------|------|------|

| Initialization Time            | t_init       |     |      | 10   | S    | 1    |

| Reset Init Assert Time         | t_reset_init |     |      | 50   | μs   | 4    |

| Serial Bus Hardware Ready Time | t_serial     |     |      | 2000 | ms   |      |

| Monitor Data Ready Time        | t_data       |     |      | 2000 | ms   |      |

| Reset Assert Time                              | t_reset     | 5   | S  | 1,3 |

|------------------------------------------------|-------------|-----|----|-----|

| LPMode Assert Time                             | ton_LPMode  | 50  | ms |     |

| LPMode De-assert Time                          | toff_LPMode | 10  | S  | 1   |

| IntL Assert Time                               | ton_IntL    | 200 | ms |     |

| IntL Deassert Time                             | toff_IntL   | 500 | μs |     |

| Rx LOS Assert Time                             | ton_lol     | 100 | ms |     |

| Tx Fault Assert Time                           | ton_Txfault | 200 | ms |     |

| Flag Assert Time                               | ton_flag    | 200 | ms |     |

| Mask Assert Time                               | ton_mask    | 100 | ms |     |

| Mask Deassert Time                             | toff_mask   | 100 | ms |     |

| Application or Rate Select<br>Change Time      | t_ratesel   | N/A | ms | 2   |

| Power_over-ride or Power-set<br>Assert Time    | ton_Pdown   | 100 | ms |     |

| Power_over-ride or Power-set<br>De-assert Time | toff_Pdown  | 10  | S  | 1   |

#### Notes:

- 1. Required for temperature stabilization; measured at room temperature condition.

- 2. This feature is unsupported.

- 3. Maximum reset hold time 100ms. If exceeded, reset assert time will be equal to initialization time.

- 4. A reset is generated by a low level longer than t\_reset\_init present on the ResetL input.

#### Timing for Squelch & Disable

| Parameter                | Symbol    | Min | Тур. | Мах | Unit | Ref. |

|--------------------------|-----------|-----|------|-----|------|------|

| Rx Squelch Assert Time   | ton_Rxsq  |     |      | 80  | μs   |      |

| Rx Squelch Deassert Time | toff_Rxsq |     |      | 80  | μs   |      |

| Tx Squelch Assert Time          | ton_Txsq   | 400 | ms | 1 |

|---------------------------------|------------|-----|----|---|

| Tx Squelch Deassert Time        | toff_Txsq  | 400 | ms | 1 |

| Tx Disable Assert Time          | ton_txdis  | 100 | ms |   |

| Tx Disable Deassert Time        | toff_txdis | 400 | ms |   |

| Rx Output Disable Assert Time   | ton_rxdis  | 100 | ms |   |

| Rx Output Disable Deassert Time | toff_rxdis | 100 | ms |   |

| Squelch Disable Assert Time     | ton_sqdis  | 100 | ms |   |

| Squelch Disable Deassert Time   | toff_sqdis | 100 | ms |   |

#### Note:

1. Not implemented by default. This feature is configurable at factory, if enabled module power consumption will increase.

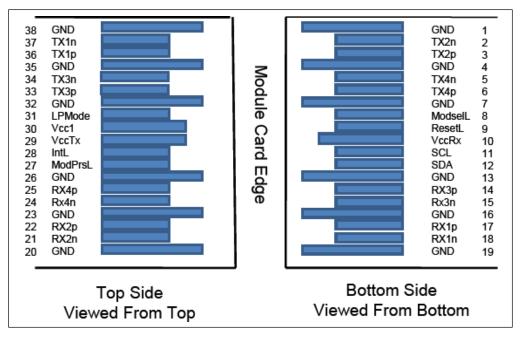

## **VII.** Pin Description

#### Figure 1 – QSFP+ Module Pad Layout

| Pin | Logic      | Symbol  | Description                         | Plug<br>Sequence | Notes |

|-----|------------|---------|-------------------------------------|------------------|-------|

| 1   |            | GND     | Ground                              | 1                | 1     |

| 2   | CML-I      | Tx2n    | Transmitter Inverted Data Input     | 3                |       |

| 3   | CML-I      | Tx2p    | Transmitter Non-Inverted Data Input | 3                |       |

| 4   |            | GND     | Ground                              | 1                | 1     |

| 5   | CML-I      | Tx4n    | Transmitter Inverted Data Input     | 3                |       |

| 6   | CML-I      | Tx4p    | Transmitter Non-Inverted Data Input | 3                |       |

| 7   |            | GND     | Ground                              | 1                | 1     |

| 8   | LVTTL-I    | ModSelL | Module Select                       | 3                |       |

| 9   | LVTTL-I    | ResetL  | Module Reset                        | 3                |       |

| 10  |            | Vcc Rx  | +3.3 V Power Supply Receiver        | 2                | 2     |

| 11  | LVCMOS-I/O | SCL     | 2-wire serial interface clock       | 3                |       |

| 12  | LVCMOS-I/O | SDA     | 2-wire serial interface data        | 3                |       |

| 13  |            | GND     | Ground                              | 1                | 1     |

# **G**FS

| 14 | CML-O   | Rx3p    | Receiver Non-Inverted Data Output   | 3 |   |

|----|---------|---------|-------------------------------------|---|---|

| 15 | CML-O   | Rx3n    | Receiver Inverted Data Output       | 3 |   |

| 16 |         | GND     | Ground                              | 1 | 1 |

| 17 | CML-O   | Rx1p    | Receiver Non-Inverted Data Output   | 3 |   |

| 18 | CML-O   | Rx1n    | Receiver Inverted Data Output       | 3 |   |

| 19 |         | GND     | Ground                              | 1 | 1 |

| 20 |         | GND     | Ground                              | 1 | 1 |

| 21 | CML-O   | Rx2n    | Receiver Inverted Data Output       | 3 |   |

| 22 | CML-O   | Rx2p    | Receiver Non-Inverted Data Output   | 3 |   |

| 23 |         | GND     | Ground                              | 1 | 1 |

| 24 | CML-O   | Rx4n    | Receiver Inverted Data Output       | 3 |   |

| 25 | CML-O   | Rx4p    | Receiver Non-Inverted Data Output   | 3 |   |

| 26 |         | GND     | Ground                              | 1 | 1 |

| 27 | LVTTL-O | ModPrsL | Module Present                      | 3 |   |

| 28 | LVTTL-O | IntL    | Interrupt                           | 3 |   |

| 29 |         | VccTx   | +3.3V Power supply transmitter      | 2 | 2 |

| 30 |         | Vcc1    | +3.3V Power supply                  | 2 | 2 |

| 31 | LVTTL-I | LPMode  | Low Power Mode                      | 3 |   |

| 32 |         | GND     | Ground                              | 1 | 1 |

| 33 | CML-I   | Тх3р    | Transmitter Non-Inverted Data Input | 3 |   |

| 34 | CML-I   | Tx3n    | Transmitter Inverted Data Input     | 3 |   |

| 35 |         | GND     | Ground                              | 1 | 1 |

| 36 | CML-I   | Tx1p    | Transmitter Non-Inverted Data Input | 3 |   |

| 37 | CML-I   | Tx1n    | Transmitter Inverted Data Input     | 3 |   |

|    |         |         |                                     |   |   |

| 38 GND Ground 1 | 1 |

|-----------------|---|

|-----------------|---|

#### Notes:

- 1. GND is the symbol for signal and supply (power) common for the QSFP+ module. All are common within the QSFP+ module and all module voltages are referenced to this potential unless otherwise noted. Connect these directly to the host board signal-common ground plane.

- 2. Vcc Rx, Vcc1 and Vcc Tx are the receiver and transmitter power supplies and shall be applied concurrently.

#### M. Recommended Boot-up Sequence

1. Host asserts LPMode input.

2. Host powers up module and module will be held in low power mode.

3. Host brings up PHY/MAC/PCS and makes sure RF signal is transmitted towards module (Comment: RF signal can be offered anywhere during boot-up.)

4. (Optional) Host checks Initialization Complete Flag (byte 06 bit 0). When "1" is read, module enters low power mode.

5. Host de-asserts LPMode input and writes "1" to High\_Power\_Class\_En bit (byte 93 bit 2), the module will enter high power mode.

6. Host delay t\_init (2s).

7. Host checks Initialization Complete Flag (byte 06 bit 0). After entering high power mode, this bit will be "1" and cleared after read. The typical timing is 5s and longest timing under extreme conditions can be up to 60s. If no "1" is read, the boot-up has failed.

8. Host reads interrupt flags (A0.02-0E including Data\_Not\_Ready flag and all of the interrupt flags) to clear IntL output during initialization.

#### Note:

1. The requirement of SFF-8636 v1.9 and higher versions is ignored and the module will boot up in high power mode regardless of power consumption.

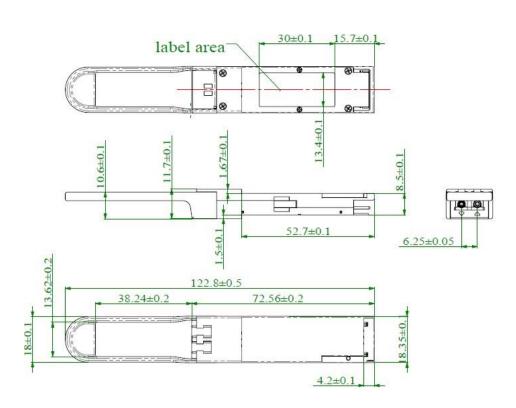

# IX. Diagram Mechanical Drawing

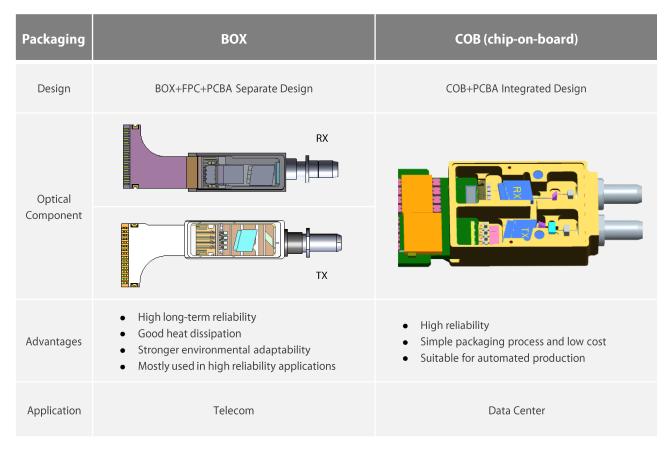

## **Core Packaging Technology**

QSFP28-LR4-100G has two types of packaging technologies which are box and chip-on-board (COB), applied in different applications due to their different advantages. The box packaging has high long-term reliability and therefore, preferably applied in transceivers for Telecom, while the COB packaging is low in cost and easy to be produced in bulk which make it a better choice for transceivers for Data Center.

## **Test Center**

FS.COM transceivers are tested to ensure connectivity and compatibility in our test center before shipped out. FS.COM test center is supported by a variety of mainstream original brand switches and groups of professional staff, helping our customers make the most efficient use of our products in their systems, network designs and deployments.

The original switches could be found nowhere but at FS.COM test center, eg: Juniper MX960 & EX 4300 series, Cisco Nexus 9396PX & Cisco ASR 9000 Series, HP 5900 Series & HP 5406R ZL2 V3(J9996A), Arista 7050S-64, Brocade ICX7750-26Q & ICX6610-48, Avaya VSP 7000 MDA 2, etc.

Cisco ASR 9000 Series(A9K-MPA-1X40GE)

Brocade ICX 7750-26Q

Dell N4032F

ARISTA 7050S-64(DCS-7050S-64)

Extreme Networks X670V VIM-40G4X

HP 5406R ZL2 V3(J9996A)

Juniper MX960

Mellanox M3601Q

AVAYA 7024XLS(7002QQ-MDA)

## **Test Assured Program**

FS.COM truly understands the value of compatibility and interoperability to each optics. Every module FS.COM provides must run through programming and an extensive series of platform diagnostic tests to prove its performance and compatibility. In our test center, we care of every detail from staff to facilities—professionally trained staff, advanced test facilities and comprehensive original-brand switches, to ensure our customers to receive the optics with superior quality.

Our smart data system allows effective product management and quality control according to the unique serial number, properly tracing the order, shipment and every part. Our in-house coding facility programs all of our parts to standard OEM specs for compatibility on all major vendors and systems such as Cisco, Juniper, Brocade, HP, Dell, Arista and so on.

With a comprehensive line of original-brand switches, we can recreate an environment and test each optics in practical application to ensure quality and distance.

The last test assured step to ensure our products to be shipped with perfect package.

## **Order Information**

| Part Number       | Description                                                             |

|-------------------|-------------------------------------------------------------------------|

| QSFP28-SR4-100G   | QSFP28 100GBASE-SR4 850nm 100m Transceiver                              |

| QSFP28-LR4-100G   | QSFP28 100GBASE-LR4 1310nm 10km Transceiver                             |

| QSFP28-PIR4-100G  | QSFP28 100GBASE-PSM4 1310nm 500m Transceiver                            |

| QSFP28-IR4-100G   | QSFP28 100GBASE-CWDM4 1310nm 2km Transceiver                            |

| QSFP28-EIR4-100G  | QSFP28 100GBASE-eCWDM4 1310nm 10km Transceiver                          |

| QSFP28-ER4-100G   | QSFP28 100GBASE-ER4 1310nm 40km Transceiver                             |

| QSFP28-LR4-100G-I | QSFP28 100GBASE-LR4 1310nm 10km Industrial Transceiver                  |

| QSFP28-LR4-100G   | QSFP28 100GBASE-LR4 and 112GBASE-OTU4 Dual Rate 1310nm 10km Transceiver |

| QSFP28-LR4-100G   | QSFP28 100GBASE-LR4 and 112GBASE-OTU4 Dual Rate 1310nm 20km Transceiver |

| QSFP28-LR4-100G   | QSFP28 100GBASE-LR4 and 112GBASE-OTU4 Dual Rate 1310nm 25km Transceiver |

| QSFP28-ER4-100G   | QSFP28 100GBASE-ER4 and 112GBASE-OTU4 Dual Rate 1310nm 30km Transceiver |

| QSFP28-ER4-100G   | QSFP28 100GBASE-ER4 and 112GBASE-OTU4 Dual Rate 1310nm 40km Transceiver |

| QSFP28-DR-100G    | QSFP28 100GBASE-DR Single Lambda 1310nm 500m Transceiver                |

| QSFP28-FR-100G    | QSFP28 100GBASE-FR Single Lambda 1310nm 2km Transceiver                 |

| QSFP28-LR-100G    | QSFP28 100GBASE-LR Single Lambda 1310nm 10km Transceiver                |

公

The information in this document is subject to change without notice. FS has made all efforts to ensure the accuracy of the information, but all information in this document does not constitute any kind of warranty.

Copyright © 2009-2022 FS.COM All Rights Reserved.