# 100G/200G DWDM Tunable CFP2 DCO 50GHz 80km DOM LC SMF Transceiver

DWDM-200CFP2-DCO

# Applications

• The 100G / 200G CFP2-DCO coherent optical module is used on the host system for MAN DWDM applications.

## Features

- 100G CFP2-DCO Coherent Optical Module 0perating up to 112.30 Gbps

- 200G CFP2-DCO Coherent Optical Module Operating up to 211.45 Gbps

- PM-QPSK (100G) and PM-16QAM (200G) Modulation Formats

- 100GE, OTU4, OTUC1 and OTUC2 Services

- Electrical Interfaces OTL4.4, OTLC1.4, CAU-I4, OTLC2.8 and CEI-28G-MR

- CFP2 MSA Hardware Specification 1.0 with Modifications Compliant

- CFP MSA Management Interface Specification 2.2 with Modifications

Compliant

- Near-End / Remote-End Data Loopback

- Hot-Pluggable CFP2 Form Factor

- Maximum Power Consumption: 24 W

## Description

The 100G / 200G CFP2-DCO coherent optical module is a high-performance, cost-effective transceiver which uses a 104-pin CFP2-MSA electrical connector for connecting the host card. The optical module consists of three functional parts: TX module, RX module and control module and has a LC optics interface and Digital diagnostics functions. They are compliant with IEEE 802.3, CFP2 MSA, CFP MSA.

## **Product Specifications**

## I. Performance Specifications

| Parameter                       | Value                                   |

|---------------------------------|-----------------------------------------|

| 100                             | DG Optical Port                         |

| Network Lane, Modulation Format | PM-QPSK                                 |

| Optical Channels                | 96                                      |

| Grid Spacing                    | 50GHz                                   |

| Frequency Range                 | 191.3 to 196.05THz                      |

| Wavelength Stability            | ± 1.5GHz                                |

| Tx Output Power, Default        | -0.5dBm                                 |

| Max. Tx Output Power            | -0.5dBm                                 |

| Min. Tx Output Power            | -6.5dBm                                 |

| Tx Output Power Accuracy        | ± 1.5dBm                                |

| Output Power During Tuning      | <-35dBm                                 |

| CD Tolerance                    | ±40000ps/nm                             |

| DGD Tolerance                   | 50ps                                    |

| Input Power Range               | 0to-18dBm                               |

| OSNR Tolerance (BOL)            | 12.5dB (Rx optical power: -8 to -10dBm) |

| Power Consumption               | Typical: 22W Maximum: 24W               |

| Parameter                       | Value                                   |

|---------------------------------|-----------------------------------------|

| 20                              | 0G Optical Port                         |

| Network Lane, Modulation Format | PM-16QAM                                |

| Optical Channels                | 96                                      |

| Grid Spacing                    | 50GHz                                   |

| Frequency Range                 | 191.3 to 196.05THz                      |

| Wavelength Stability            | ± 1.5GHz                                |

| Tx Output Power, Default        | -0.5dBm                                 |

| Max. Output Optical Power       | -0.5dBm                                 |

| Min. Tx Output Power            | -6.5dBm                                 |

| Tx Output Power Accuracy        | ± 1.5dBm                                |

| Output Power During Tuning      | <-35dBm                                 |

| CD Tolerance                    | ±40000ps/nm                             |

| DGD Tolerance                   | 22ps                                    |

| Input Power Range               | 0to-18dBm                               |

| OSNR Tolerance (BOL)            | 18.5dB (Rx Optical Power: -8 to -10dBm) |

| Power Consumption               | Typical: 22W<br>Maximum: 24W            |

# II. Absolute Maximum Ratings

| Parameter           | Min. | Max. | Unit |

|---------------------|------|------|------|

| Storage Temperature | -40  | 85   | ٥C   |

| Parameter                                                         | Min. | Max.                                     | Unit |

|-------------------------------------------------------------------|------|------------------------------------------|------|

| Operating Case Temperature                                        | 0    | 70                                       | ٥C   |

| Relative Humidity, Operating (non-condensing)                     | 5    | 85                                       | %    |

| Relative Humidity, Operating (Shortterm<96hrs,<br>Non-Condensing) | 5    | 95                                       | %    |

| ESD Sensitivity (HBM)                                             |      | High-Speed Pins:<br>1000 Other Pins:2000 | V    |

## **III. Electrical Characteristics**

## **1. Power Supply Requirements**

The 100G / 200G CFP2 coherent optical module is powered by an independent 3.3 V power supply on the host. All voltages are tested at the connector interfaces.

| Parameter                    | Symbol          | Min. | Typical | Max. | Unit | Note      |

|------------------------------|-----------------|------|---------|------|------|-----------|

| 3.3V DC Power Supply Voltage | V <sub>cc</sub> | 3.2  | 3.3     | 3.4  | V    | ±5%       |

| 3.3V DC Power Supply Current | I <sub>cc</sub> |      |         | 7.3  | А    | Note1&2   |

| Power Supply Noise           | Vrip            |      |         | 2    | %p-p | DC-1MHz   |

| Power Supply Noise           |                 |      |         | 3    |      | 1-10MHz   |

| Power Consumption            | Pw_class 4      |      | 22      | 24   | W    | 200G Mode |

| Operating Temperature        | т               | 0    |         | 70   | ٥C   |           |

Note:

1. The Min. and Max. values apply to the full temperature range at the EOL of the module. Typical values (Typ.) are defined at the BOL of the module, with operating temperature at 25°C and expected power supplied.

2. The maximum current of each pin cannot exceed 1.3 A.

3. The Max. value of Icc is for design reference, and the expected working current cannot exceed Pw\_normal/Vcc.

## 2. High-Speed Electrical Interface Specifications

## 2.1 Transmitter Data (TX)

The transmitter data signal complies with the CEI-28G-MR low swing standards.

#### 2.2 Receiver Data (RX)

The receiver data signal complies with the CEI-28G-MR standards.

#### 2.3 Reference Clock (REFCLK)

The host does not need to provide a reference clock (REFCLK) for the 100G / 200G CFP2-DCO coherent optical module, because a 622.08M local clock is integrated in the 200G CFP2-DCO coherent optical module.

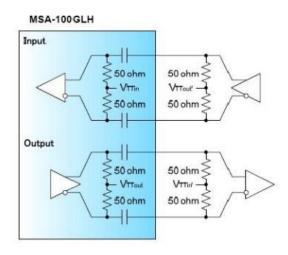

Figure 1. High-Speed I/O for Data and Clocks

#### 2.4 Transmitter Monitor Clock (TXMCLK)

The transmitter of the 100G / 200G CFP2-DCO coherent optical module provides a monitoring clock TXMCLK, which is mainly used as a reference for monitoring optical signals at the transmitter. The clock can be used to trigger a high-speed sampling oscilloscope.

| Parameter                                       | Symbol  | Min. | Typical | Max. | Unit | Note                                                                      |

|-------------------------------------------------|---------|------|---------|------|------|---------------------------------------------------------------------------|

| Impedance                                       | Zd      | 80   | 100     | 120  | Ω    |                                                                           |

| Transmitter Monitor Clock<br>Frequency (TXMCLK) |         |      | 1/ 48   |      | Hz   | The Frequency is1/48 the Symbol Rate of the Transmitter's Optical Signal. |

| TXMCLK Differential Voltage                     | VDIFFTX | 500  |         | 1000 | mV   | Differential Peak-to-Peak Voltage                                         |

## **3.Control Pins (non-MDIO) Functional Description**

## 3.1 TX\_DIS (Transmitter Disable)

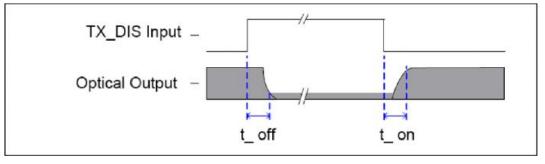

TX\_DIS is an input pin which receives signals from the host and operates in the logic high state. When TX\_DIS is logic high, the output optical signal inside the optical module is turned off. When TX\_DIS is logic low, the output optical signal inside the optical module is turned on. The symbol "t\_on" is the turn-on time and "t\_off" is the turn-off time. Figure 4-2 shows the timing diagram.

Figure 2. Timing Diagram for TX\_DIS

#### 3.2 MOD\_LOPWR (Module Low Power)

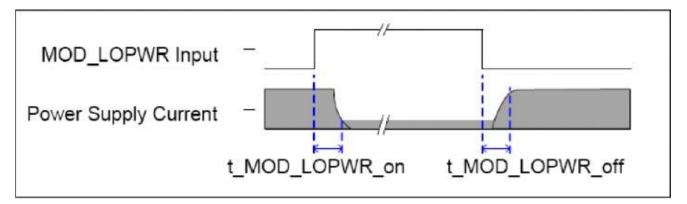

MOD\_LOPWR is an input pin which receives signals from the host and works in the logic high state. When MOD\_LOPWR is logic high, the optical module works at low power consumption and remains in this mode. When MOD\_LOPWR is pulled down, the optical module is initialized to a high power consumption state, that is, the normal operation mode. In low power consumption mode, the optical module communicates through the MDIO management interface, and its maximum power consumption does not exceed 2 W. Figure 4-3 shows the values of "t\_MOD\_LOPWR\_on" and "t\_MOD\_LOPWR\_off".

Figure 3. Timing Diagram for MOD\_LOPWR

#### 3.3 MOD\_RSTn (Module Reset)

MOD\_RSTn is an input pin which receives signals from the host and works in the logic low state. When MOD\_RSTn is pulled low, the optical module is in the reset state. When MOD\_RSTn is logic high, the optical module exits the reset mode and starts power-on initialization.

## 4. Alarm Pins (non-MDIO) Functional Description

#### 4.1 RX\_LOS (Receiver Loss of Signal)

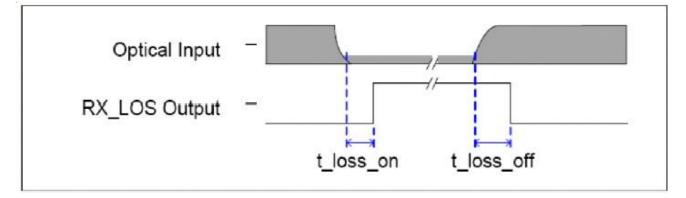

RX\_LOS is an output pin which transmits signals to the host and works at the logic high state. When RX\_LOS is logic high, the optical power received by the optical module is too low. Figure 4-4 shows the timing diagram for RX\_LOS.

Figure 4. Timing Diagram for RX\_LOS

#### 4.2 MOD\_ABS (Module Absent)

MOD\_ABS is an output pin which transmits signals from the inside of the module to the host. This pin is pulled up on the host and pulled down to the ground inside the module. When the optical module is inserted into the host, MOD\_ABS is logic low, meaning that the module is present. When the optical module is absent on the host, MOD\_ABS is logic high, meaning that the module is absent.

## 5. Control and Alarm Descriptions

## 5.1 Timing Parameters for Control and Alarm Signals

| Parameter                              | Symbol               | Min. | Max. | Unit |

|----------------------------------------|----------------------|------|------|------|

| Transmitter Disabled (TX_DIShigh)      | t_off                |      | 1    | ms   |

| Transmitter Enabled(TX_DISlow)         | t_on                 |      | 25   | S    |

| MOD_LOPWR Assert                       | t_MOD_LOPWR_assert   |      | 25   | S    |

| MOD_LOPWR Deassert                     | t_MOD_LOPWR_deassert |      | 25   | S    |

| Receiver Loss of Signal Assert Time    | t_loss_on            |      | 1    | ms   |

| Receiver Loss of Signal De-assert Time | t_loss_off           |      | 15   | ms   |

| Initialization Time from Reset         | t_initialize         | 190  | 220  | S    |

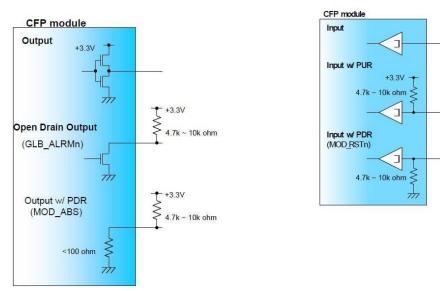

#### 5.2 V LVCMOS Electrical Characteristics

The 3.3 V LVCMOS level of the hardware control and alarm signal pins described above shall meet the electrical characteristics described in Table 4-6. Figure 4-5 shows the recommended input and output termination modes for these pins.

| Parameter                            | Symbol          | Min.                 | Typical | Max.    | Unit |

|--------------------------------------|-----------------|----------------------|---------|---------|------|

| Power Supply Voltage                 | V <sub>cc</sub> | 3.2                  | 3.3     | 3.4     | V    |

| Input High Voltage                   | VIH             | 2                    |         | VCC+0.3 | V    |

| Input Low Voltage                    | VIL             | -0.3                 |         | 0.8     | V    |

| Input Leakage Current                | IIN             | -10                  |         | 10      | μΑ   |

| Output High Voltage<br>(IOH=-100 μA) | VOH             | V <sub>CC</sub> -0.2 |         |         | V    |

| Output Low Voltage<br>(IOL=100µA)    | VOL             |                      |         | 0.2     | V    |

Figure 5. Reference 3.3 V LVCMOS Input / Output Termination

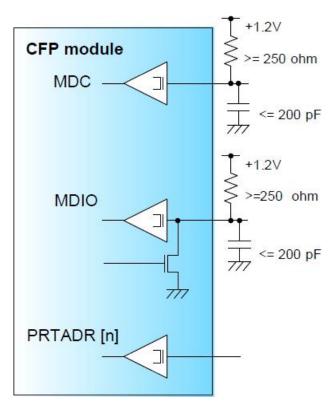

## 6. Module Management Interface Pins (MDIO) Description

## 6.1 Management Data Input / Output (MDIO) Interface

The MDIO implementation is defined in IEEE 802.3 clause 45. The optical module supports a lane rate of up to 4 Mb/s. The MDIO of the optical module uses the 1.2 V LVCMOS logic level.

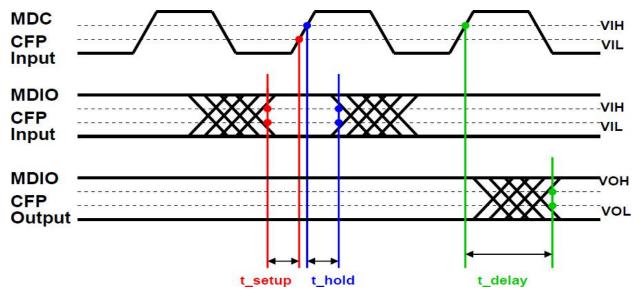

## 6.2 Management Data Clock (MDC) Interface Pins

The host defines that the maximum MDC rate can reach 4 MHz, so the maximum MDC rate that the optical module supports can reach 4 MHz. Figure 4-6 shows the timing diagram for the MDIO and MDC pins. The optical module should follow the minimum setup time "tsetup" and hold time "thold" requirements of the MDIO port supplementary protocol.

Figure 6. Timing Diagram for the MDIO & MDC Interfaces

#### 6.3 MDIO Physical Port Address Pins (PRTADRs)

The PRTADRs are used by the host system to assign addresses to all optical modules belonging to its management area. PREADR0 corresponds to the LSB of the physical port address bit. The host drives the physical port address line of 5pin to set the physical port address of the optical module by following the address protocol of the MDIO port. It is recommended that these physical port addresses should not change when the optical module is powered on.

## 6.4 V LVCMOS Electrical Characteristics

| Parameter                        | Symbol | Min. | Max. | Unit |

|----------------------------------|--------|------|------|------|

| Input High Voltage               | VIH    | 0.84 | 1.5  | V    |

| Input Low Voltage                | VIL    | -0.3 | 0.36 | V    |

| Input Leakage Current            | IIN    | -100 | 100  | μΑ   |

| Output High Voltage (IOH=-100μA) | VOH    | 1    | 1.5  | V    |

| Output Low Voltage (IOL=100μA)   | VOL    | -0.3 | 0.2  | V    |

| Output High Current              | ЮН     |      | -4   | mA   |

| Output Low Current               | IOL    | +4   |      | mA   |

| Input Capacitance                | Ci     |      | 10   | pF   |

Figure 7. Reference MDIO Interface Termination

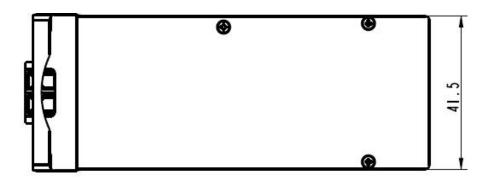

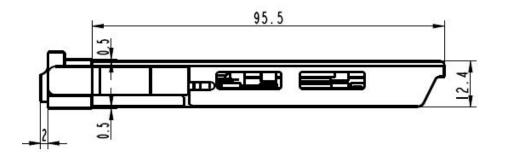

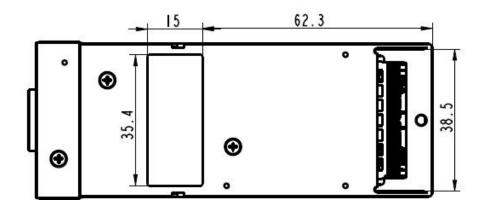

## **IV. Mechanical Specifications**

the mechanical dimensions of the 100G / 200G CFP2-DCO coherent optical module. Max. dimensions (L  $\times$  W  $\times$  H): 107.5 mm  $\times$  42.5 mm  $\times$  13.4 mm

Figure 8. Mechanical Dimensions of the CFP2 Optical Module

**G**FS

# V. Pin Description

| Pin | Name                           | I/O | Logic           | Description                                                                                                                                                             |

|-----|--------------------------------|-----|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | GND                            |     |                 |                                                                                                                                                                         |

| 2   | (TX_MCLKn) or<br>Vendor_Out 0n | 0   | CML             | For optical waveform testing or Module vendor output                                                                                                                    |

| 3   | (TX_MCLKp) or<br>Vendor_Out 0p | 0   | CML             | For optical waveform testing or Module vendor output                                                                                                                    |

| 4   | GND                            |     |                 |                                                                                                                                                                         |

| 5   | Vendor_In 0n                   | I   | CML             | Module vendor input. Vendor specific.                                                                                                                                   |

| 6   | 5 Vendor_In 0n                 | I   | CML             | Module vendor input. Vendor specific.                                                                                                                                   |

| 7   | 3.3V_GND                       |     |                 | 3.3V Module Supply Voltage Return Ground, can be separate or tied together with Signal Ground                                                                           |

| 8   | 3.3V_GND                       |     |                 |                                                                                                                                                                         |

| 9   | 3.3V                           |     |                 | 3.3V Module Supply Voltage                                                                                                                                              |

| 10  | 3.3V                           |     |                 |                                                                                                                                                                         |

| 11  | 3.3V                           |     |                 |                                                                                                                                                                         |

| 12  | 3.3V                           |     |                 |                                                                                                                                                                         |

| 13  | 3.3V_GND                       |     |                 |                                                                                                                                                                         |

| 14  | 3.3V_GND                       |     |                 |                                                                                                                                                                         |

| 15  | CML-O                          | I/O |                 | Module Vendor I/O A. Do Not Connect!                                                                                                                                    |

| 16  | 5 VND_IO_A                     | I/O |                 | Module Vendor I/O B. Do Not Connect!                                                                                                                                    |

| 17  | PRG_CNTL1                      | I   | LVCMOS<br>w/PUR | Programmable Control 1 set over MDIO, MSA Default:<br>TRXIC_RSTn, TX & RX ICs reset, "0": reset, "1" or NC: enabled =<br>not used                                       |

| 18  | PRG_CNTL2                      | I   | LVCMOS<br>w/PUR | Programmable Control 2 set over MDIO, MSA Default: Hardware<br>Interlock LSB, "00": $\leq$ 9W, "01": $\leq$ 12W, "10": $\leq$ 15W, "11" or NC:<br>$\leq$ 18W = not used |

| Pin | Name      | I/O | Logic           | Description                                                                                                                                                             |

|-----|-----------|-----|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 19  | PRG_CNTL3 | I   | LVCMOS<br>w/PUR | Programmable Control 3 set over MDIO, MSA Default: Hardware<br>Interlock MSB, "00": $\leq$ 9W, "01": $\leq$ 12W, "10": $\leq$ 15W, "11" or NC:<br>$\leq$ 18W = not used |

| 20  | PRG_ALRM1 | 0   | LVCMOS          | Programmable Alarm 1 set over MDIO, MSA Default: HIPWR_ON,<br>"1": module power up completed, "0": module not high powered up                                           |

| 21  | PRG_ALRM2 | 0   | LVCMOS          | Programmable Alarm 2 set over MDIO, MSA Default:<br>MOD_READY, "1": Ready, "0": not Ready                                                                               |

| 22  | PRG_ALRM3 | 0   | LVCMOS          | Programmable Alarm 3 set over MDIO, MSA Default: MOD_FAULT,<br>fault detected, "1": Fault, "0": No Fault                                                                |

| 23  | GND       |     |                 |                                                                                                                                                                         |

| 24  | TX_DIS    | I   | LVCMOS<br>w/PUR | Transmitter Disable for all lanes, "1" or NC = transmitter disabled,<br>"0" = transmitter enabled                                                                       |

| 25  | RX_LOS    | 0   | LVCMOS          | Receiver Loss of Optical Signal, "1": low optical signal, "0": normal condition                                                                                         |

| 26  | MOD_LOPWR | I   | LVCMOS<br>w/PUR | Module Low Power Mode. "1" or NC: module in low power (safe)<br>mode, "0": power-on enabled                                                                             |

| 27  | MOD_ABS   | 0   | GND             | Module Absent. "1" or NC: module absent, "0": module present, Pull<br>Up Resistor on Host                                                                               |

| 28  | MOD_RSTn  | I   | LVCMOS<br>w/PDR | Module Reset. "0" resets the module, "1" or NC = module enabled,<br>Pull Down Resistor in Module                                                                        |

| 29  | GLB_ALRMn | 0   | LVCMOS          | Global Alarm. "0": alarm condition in any MDIO Alarm register, "1":<br>no alarm condition, Open Drain, Pull Up Resistor on Host                                         |

| 30  | GND       |     |                 |                                                                                                                                                                         |

| 31  | MDC       | I   | 1.2V<br>CMOS    | Management Data Clock (electrical specs as per IEEE Std 802.3-<br>2012)                                                                                                 |

| 32  | MDIO      | I/O | 1.2V<br>CMOS    | Management Data I/O bi-directional data (electrical specs as per<br>IEEE Std 802.3-2012)                                                                                |

| 33  | 3 PRTADR0 | I   | 1.2V<br>CMOS    | MDIO Physical Port address bit 0                                                                                                                                        |

| 34  | PRTADR1   | I   | 1.2V<br>CMOS    | MDIO Physical Port address bit 1                                                                                                                                        |

| 35  | PRTADR2   | I   | 1.2V<br>CMOS    | MDIO Physical Port address bit 2                                                                                                                                        |

| 36  | VND_IO_C  | I/O |                 | Module Vendor I/O C. Do Not Connect!                                                                                                                                    |

| Pin | Name                          | I/O | Logic | Description                                          |

|-----|-------------------------------|-----|-------|------------------------------------------------------|

| 37  | VND_IO_D                      | I/O |       | Module Vendor I/O D. Do Not Connect!                 |

| 38  | VND_IO_E                      | I/O |       | Module Vendor I/O E. Do Not Connect!                 |

| 39  | 3.3V_GND                      |     |       |                                                      |

| 40  | 3.3V_GND                      |     |       |                                                      |

| 41  | 3.3V                          |     |       | 3.3V Module Supply Voltage                           |

| 42  | 3.3V                          |     |       |                                                      |

| 43  | 3.3V                          |     |       |                                                      |

| 44  | 3.3V                          |     |       |                                                      |

| 45  | 3.3V_GND                      |     |       |                                                      |

| 46  | 3.3V_GND                      |     |       |                                                      |

| 47  | Vendor_In1n                   | I   | CML   | Module vendor input                                  |

| 48  | Vendor_In1p                   | I   | CML   | Module vendor input                                  |

| 49  | GND                           |     |       |                                                      |

| 50  | (RX_MCLKn) or<br>Vendor_Out1n | 0   | CML   | For optical waveform testing or Module vendor output |

| 51  | (RX_MCLKn) or<br>Vendor_Out1p | 0   | CML   | For optical waveform testing or Module vendor output |

| 52  | GND                           |     |       |                                                      |

## **Test Center**

# I. Compatibility Testing

Each fiber optical transceiver has been tested in host device on site in FS Assured Program to ensure full compatibility with over 200 vendors.

Cisco Catalyst C9500-24Y4C

Cisco MS425-16

Brocade VDX 6940-144S

Dell EMC Networking Z9100-ON

Force<sup>10</sup>tm S60-44T

HUAWEI S6720-30L-HI-24S

Above is part of our test bed network equipment. For more information, please click the <u>Test Bed PDF</u>. It will be updated in real time as we expand our portfolio.

## **II. Performance Testing**

Each fiber optical transceiver has been fully tested in FS Assured Program equipped with world's most advanced analytical equipment to ensure that our transceivers work perfectly on your device.

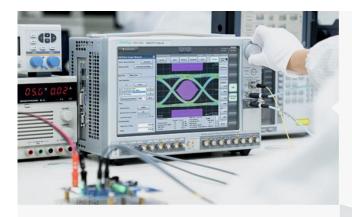

## 1. TX/RX Signal Quality Testing

Equipped with the all-in-one tester integrated 4ch BERT & sampling oscilloscope, and variable optical attenuator to ensure the input and output signal quality.

- Eye Pattern Measurements: Jitter, Mask Margin, etc

- Average Output Power

- OMA

- Extinction Ratio

- Receiver Sensitivity

- BER Curve

#### 2. Reliability and Stability Testing

Subject the transceivers to dramatic changes in temperature on the thermal shock chamber to ensure reliability and stability of the transceivers.

- Commercial: 0 °C to 70 °C

- Extended: -5 °C to 85 °C

- Industrial: -40 °C to 85 °C

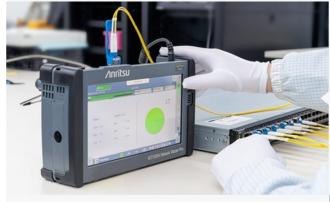

#### 3. Transfer Rate and Protocol Testing

Test the actual transfer data rate and the transmission ability under different protocols with Network Master Pro.

- Ethernet

- Fibre Channel

- SDH/SONET

- CPRI

#### 4. Optical Spectrum Evaluation

Evaluate various important parameters with the Optical Spectrum Analyzer to meet the industry standards.

- Center Wavelength, Level

- OSNR

- SMSR

- Spectrum Width

# **Ordering Information**

| Part Number      | Description                                                      |

|------------------|------------------------------------------------------------------|

| QSFP56-SR4-200G  | 200GBASE-SR4 QSFP56 850nm 100m DOM MTP/MPO Transceiver for MMF   |

| QSFP56-FR4-200G  | 200GBASE-FR4 QSFP56 1310nm 2km DOM LC Transceiver for SMF        |

| QSFP56-LR4-200G  | 200GBASE-LR4 QSFP56 1310nm 10km DOM LC Transceiverfor SMF        |

| QSFPDD-2SR4-200G | 200GBASE-2SR4 QSFP-DD 850nm 100m DOM MTP/MPO Transceiver for MMF |

17

The information in this document is subject to change without notice. FS has made all efforts to ensure the accuracy of the information, but all information in this document does not constitute any kind of warranty.

Copyright © 2009-2022 FS.COM All Rights Reserved.